Nyheter

En utsikt fra RISC-V-toppmøtet

Det var to kunngjøringer fra IAR Systems til støtte for å etablere et robust økosystem for RISC-V. Den første var med IP-leverandøren, SiFive, for å samarbeide om å bringe førstnevnte kompilator- og feilsøkingsverktøy til den konfigurerbare prosessorkjerne-IP.

Integrasjon av verktøy og IP forventes å støtte utviklere til å levere produkter og øke distribusjonen av den åpne, gratis instruksjonssettarkitekturen (ISA).

Anders Holmberg, Chief Strategy Officer, IAR Systems, sa målet er å hjelpe utviklere med å øke produktiviteten og fokusere på innovasjon. "SiFive er ledende innen kommersiell RISC-V core IP, og vår verktøykjede IAR Embedded Workbench er den mest brukte verktøykjeden for å bygge innebygde applikasjoner," sa han. Aksenten er på skalerbar, effektiv tilpasset silisium og utviklingsverktøy for å møte arbeidsmengder.

IAR innebygd arbeidsbenk for RISC-V vil være tilgjengelig medio 2019. Verktøykjeden hevder å tilby "ledende kodekvalitet, størrelse og hastighet" samt en integrert feilsøking med støtte for simulator og maskinvarefeilsøking.

Programvareselskapet kunngjorde også et samarbeid med CPU IP-leverandøren, Andes, for å støtte selskapets RISC-V-kjerner, AndesCore N25 (F) / NX25 (F) og A25 / AX25, i IAR Embedded Workbench for RISC-V. Den første versjonen vil være tilgjengelig i midten av 2019. AndeStar V5 instruksjonsutvidelse og ACE-instruksjoner for tilpasning av instruksjoner kan kobles til arbeidsbenk for å maksimere kodehastighet og minimere kodestørrelse for RISC-V kjerner.

Automatisering og sanntids databehandling

Den siste versjonen av verktøypakken og en ny EOSC-V-kjerne optimalisert for Linux og sanntids databehandling ble kunngjort av Codasip.

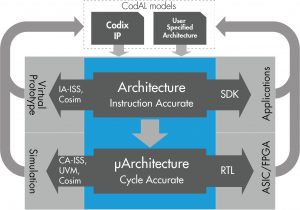

Studio 8-verktøyverktøyet gjør det mulig for utviklere å skrive en beskrivelse på høyt nivå av en prosessor og syntetiserer designet (bildet) automatisk.

"Etter hvert som RISC-V ISA-spesifikasjonen utvikler seg og legger til et stadig økende antall valgfrie arkitekturutvidelser, blir en prosessordesignmetodikk som gir mulighet for både rask arkitektonisk utforskning og forenklet opprettelse av lett implementerbare RTL," observert Chris Jones, visepresident for Markedsføring hos Codasip. "Det som trengs er et prosessorbeskrivelsesspråk på høyt nivå som er optimalisert for RISC-V," la han til og introduserte verktøypakken.

Prosessorbeskrivelsen er skrevet i CodAL, et arkitekturbeskrivelsesspråk, og deretter blir designets RTL, testbenk, virtuelle plattformmodeller og prosessorprogramvareutviklingssett (C / C ++ -kompilator, debugger, profiler) automatisk syntetisert. Metodikken reduserer tidsbruken på å opprettholde et komplett programvareutviklingssett (SDK) ved å bruke en instruksjonsnøyaktig (IA) prosessormodell i CodAL til Time som ellers ville være nødvendig for å opprettholde en komplett SDK og implementeringen er betydelig redusert takket være metodikken som bruker en instruksjonsnøyaktig (IA) prosessormodell i CodAL for SDK-generering og en syklusnøyaktig modell for implementering.

Ny funksjonalitet og funksjoner for åttende generasjons verktøypakke inkluderer støtte for en LLVM-feilsøking og OpenOCB, Studio / CodeSpace integrerte utviklingsmiljøer (IDEer) basert på Eclipse Oxygen og mer interaktive konsoller og forbedringer av testsuiter og verifisering for å støtte brukerdefinerte RISC -V utvidelser.

Selskapet introduserte også den 64-biters Bk7-prosessoren, og bidro til Bk-familien. Den har en syv-trinns rørledning med grenprediksjon, valgfri full minnehåndteringsenhet (MMU) med virtuell adresseringsstøtte for operativsystemer som Linux, populære RISC-V standardutvidelser og eksterne standardgrensesnitt for industrien.

Det er selskapets hittil ytelsesprosessor og kan tilpasses for utviklere å legge til instruksjoner, registre eller grensesnitt.

Studio 8 og Bk7-prosessoren vil være generelt tilgjengelig Q1 2019, med tidlig tilgang til utvalgte kunder umiddelbart.

Microchip kunngjorde at den legger til det den mener er bransjens første RISC-V SoC FPGA-arkitektur til Mi-V-økosystemet. FPGA-ene kombinerer Microsemiconductor PolarFire FPGA-er og et mikroprosessorundersystem basert på RISC-V ISA.

I forkant av toppmøtet kunngjorde Linux Foundation samarbeidet med RISC-V Foundation for å fremskynde åpen kildekodeutvikling og adopsjon av RISC-V ISA.