新聞動態

RISC-V峰會的觀點

IAR Systems發布了兩個公告,以支持為RISC-V建立一個強大的生態系統。第一個是與IP提供商SiFive合作,將前者的編譯器和調試器工具引入可配置的處理器核心IP。

工具和IP的集成有望支持開發人員交付產品並增加開放,免費的指令集體系結構(ISA)的部署。

IAR Systems首席戰略官Anders Holmberg表示,其目的是幫助開發人員提高生產力並專注於創新。他說:“ SiFive是商業RISC-V核心IP的領導者,我們的工具鏈IAR嵌入式工作台是構建嵌入式應用程序使用最廣泛的工具鏈。”重點是可擴展,高效的定制芯片和開發工具,以滿足計算工作負載。

適用於RISC-V的IAR嵌入式工作台將於2019年中推出。該工具鏈聲稱提供“領先的代碼質量,大小和速度”,以及具有模擬器和硬件調試支持的集成調試器。

該軟件公司還宣布與CPU IP供應商Andes建立合作關係,以在RISC-V的IAR嵌入式工作台中支持該公司的RISC-V內核,AndesCore N25(F)/ NX25(F)和A25 / AX25。首個版本將於2019年中推出。 AndeStar V5指令擴展和Andes自定義擴展(ACE)指令自定義功能將與Workbench結合使用,以最大化RISC-V內核的代碼速度並最小化代碼大小。

自動化和實時計算

Codasip宣布了其工具套件的最新版本以及針對Linux和實時計算進行了優化的新EOSC-V內核。

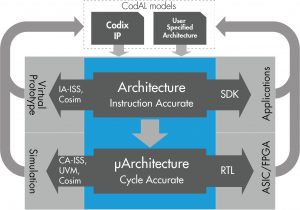

其Studio 8工具套件允許開發人員編寫處理器的高級描述並自動綜合設計(如圖)。

“隨著RISC-V ISA規範的發展並添加了越來越多的可選體系結構擴展,一種能夠快速進行體系結構探索並簡化可輕鬆實現的RTL的創建的處理器設計方法就變得至關重要,”該公司副總裁Chris Jones說道。 Codasip的市場營銷。他補充說:“需要的是針對RISC-V優化的高級處理器描述語言。”

處理器說明使用架構描述語言CodAL編寫,然後自動綜合設計的RTL,測試平台,虛擬平台模型和處理器軟件開發套件(C / C ++編譯器,調試器,分析器)。通過使用CodAL to Time中的指令精確(IA)處理器模型,該方法可減少維護完整軟件開發套件(SDK)所花費的時間,否則該模型將需要維護完整的SDK,並且由於使用了該方法,因此大大減少了實現CodAL中用於SDK生成的指令精確(IA)處理器模型和用於實施的周期精確模型。

第八代工具套件的新功能包括:支持LLVM調試器和OpenOCB,基於Eclipse Oxygen的Studio / CodeSpace集成開發環境(IDE)和更多交互式控制台,以及對測試套件和驗證的改進,以支持用戶定義的RISC -V擴展名。

該公司還推出了64位Bk7處理器,從而增加了Bk系列。它具有一個具有分支預測功能的七階段管道,可選的全內存管理單元(MMU),並具有對Linux等操作系統的虛擬尋址支持,流行的RISC-V標準擴展和行業標準外部接口。

它是該公司迄今為止性能最高的處理器,可以為開發人員定制以添加指令,寄存器或接口。

Studio 8和Bk7處理器將在2019年第一季度全面上市,並立即搶先提供給部分客戶。

Microchip宣布將在其Mi-V生態系統中添加其認為是業界首個RISC-V SoC FPGA架構的產品。該FPGA結合了微半導體PolarFire FPGA和基於RISC-V ISA的微處理器子系統。

在峰會召開之前,Linux基金會宣布與RISC-V基金會合作,以加快開源開發和RISC-V ISA的採用。