Новини

Изглед от срещата на върха RISC-V

Имаше две съобщения от IAR Systems в подкрепа на създаването на здрава екосистема за RISC-V. Първият беше с IP доставчика, SiFive, за да сътрудничи за привеждане на бившите инструменти за компилация и отстраняване на грешки до конфигурируемия IP процесор на ядрото.

Очаква се интеграцията на инструменти и IP да подпомогне разработчиците да доставят продукти и да увеличи разгръщането на отворената, безплатна архитектура на набор от инструкции (ISA).

Андерс Холмберг, главен директор по стратегията на IAR Systems, заяви, че целта е да се помогне на разработчиците да повишат производителността и да се съсредоточат върху иновациите. „SiFive е лидер в областта на комерсиалния IP RISC-V и нашата инструментална мрежа IAR Embedded Workbench е най-използваната верига инструменти за изграждане на вградени приложения“, каза той. Акцентът е върху мащабируеми, ефективни персонализирани силиций и инструменти за разработка, за да се отговори на изчисленията на натоварването.

IAR Embedded Workbench за RISC-V ще бъде наличен в средата на 2019 г. Инструменталната верига твърди, че предлага „водещо качество, размер и скорост на кода“, както и интегриран отладчик със симулатор и хардуерна поддръжка за отстраняване на грешки.

Софтуерната компания също обяви партньорство с IP доставчика на процесора, Andes, за да подкрепи ядрата на RISC-V на компанията, AndesCore N25 (F) / NX25 (F) и A25 / AX25, в IAR Embedded Workbench за RISC-V. Първата версия ще бъде налична в средата на 2019 г. Разширението за инструкции за AndeStar V5 и възможностите за персонализиране на инструкциите на Andes Custom Extension (ACE) ще бъдат съчетани с Workbench, за да се увеличи максимално скоростта на кода и да се сведе до минимум размерът на кода за RISC-V ядра.

Автоматизация и изчисления в реално време

Най-новата версия на своя набор от инструменти и ново ядро EOSC-V, оптимизирано за Linux и изчисления в реално време, бяха обявени от Codasip.

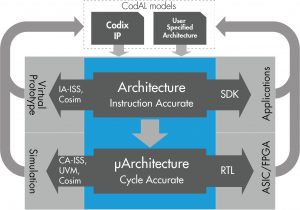

Комплектът му Studio 8 позволява на разработчиците да напишат описание на процесор на високо ниво и автоматично синтезира дизайна (на снимката).

„Тъй като спецификацията на RISC-V ISA се развива и добавя непрекъснато нарастващ брой незадължителни архитектурни разширения, методологията за проектиране на процесори, която позволява както бързо архитектурно проучване, така и опростено създаване на лесно изпълним RTL, става от съществено значение“, отбеляза Крис Джоунс, вицепрезидент на Маркетинг в Codasip. „Необходим е език за описание на процесори на високо ниво, оптимизиран за RISC-V“, добави той, представяйки пакета с инструменти.

Описанието на процесора е написано на CodAL, език за описание на архитектурата, след което автоматично се синтезират RTL, тестовият стенд, моделите за виртуална платформа и разработвания софтуер за процесор (C / C ++ компилатор, отладчик, профилер) на дизайна. Методиката намалява времето, изразходвано за поддържане на пълен комплект за разработка на софтуер (SDK), като се използва модел с процесор точен (IA) процесор в CodAL to Time, който в противен случай би бил необходим за поддържане на пълен SDK и прилагането е значително намалено благодарение на методологията, която използва модел на процесор точен (IA) процесор в CodAL за генериране на SDK и точен цикъл модел за внедряване.

Новата функционалност и функции за пакета от инструменти за осмо поколение включват поддръжка за отладчик LLVM и OpenOCB, Studio / CodeSpace интегрирани среди за разработка (IDE), базирани на Eclipse Oxygen, и повече интерактивни конзоли и подобрения на тестовите пакети и проверка в подкрепа на зададения от потребителя RISC -V разширения.

Компанията също представи 64-битовия Bk7 процесор, добавяйки към семейството Bk. Той има седемстепенен тръбопровод с предсказване на клонове, опционално устройство за управление на пълната памет (MMU) с поддръжка за виртуално адресиране на операционни системи като Linux, популярни стандартни разширения RISC-V и стандартни отраслови външни интерфейси.

Това е най-ефективният процесор на компанията до момента и е персонализиран за разработчиците да добавят инструкции, регистри или интерфейси.

Студио 8 и Bk7 процесорът ще бъдат общодостъпни през първото тримесечие на 2019 г. с ранен достъп до избрани клиенти веднага.

Microchip обяви, че добавя това, което според него е първата в индустрията RISC-V SoC FPGA архитектура към своята Mi-V екосистема. FPGAs комбинират Microsemiconductor PolarFire FPGAs и микропроцесорна подсистема, базирана на RISC-V ISA.

Преди срещата на върха Фондацията Linux обяви сътрудничеството си с Фондация RISC-V за ускоряване на разработването с отворен код и приемането на ISA RISC-V.