Informações

Vista da Cúpula RISC-V

Houve dois anúncios da IAR Systems em apoio ao estabelecimento de um ecossistema robusto para o RISC-V. O primeiro foi com o provedor de IP, SiFive, para colaborar com o fornecimento das ferramentas de compilação e depuração do ex para o IP do núcleo do processador configurável.

Espera-se que a integração de ferramentas e IP ofereça suporte aos desenvolvedores na entrega de produtos e aumente a implantação da arquitetura aberta e gratuita do conjunto de instruções (ISA).

Anders Holmberg, diretor de estratégia da IAR Systems, disse que o objetivo é ajudar os desenvolvedores a aumentar a produtividade e se concentrar na inovação. "A SiFive é líder em IP comercial RISC-V, e nossa IAR Embedded Workbench da cadeia de ferramentas é a cadeia de ferramentas mais amplamente usada para a construção de aplicativos incorporados", disse ele. O destaque é para ferramentas de desenvolvimento e silício personalizadas eficientes e escalonáveis para atender às cargas de trabalho de computação.

O IAR Embedded Workbench para RISC-V estará disponível em meados de 2019. A cadeia de ferramentas alega oferecer "qualidade, tamanho e velocidade de código líderes", além de um depurador integrado com suporte a simulador e depuração de hardware.

A empresa de software também anunciou uma parceria com o provedor de IP da CPU, Andes, para apoiar os núcleos RISC-V da empresa, os AndesCore N25 (F) / NX25 (F) e A25 / AX25, no IAR Embedded Workbench para RISC-V. A primeira versão estará disponível em meados de 2019. A extensão de instrução AndeStar V5 e os recursos de personalização da instrução Andes Custom Extension (ACE) serão acoplados ao Workbench para maximizar a velocidade do código e minimizar o tamanho do código para os núcleos RISC-V.

Automação e computação em tempo real

A versão mais recente de seu conjunto de ferramentas e um novo núcleo EOSC-V otimizado para Linux e computação em tempo real foram anunciados pela Codasip.

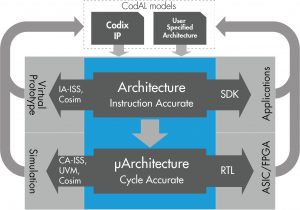

Seu conjunto de ferramentas Studio 8 permite que os desenvolvedores escrevam uma descrição de alto nível de um processador e sintetizam automaticamente o design (foto).

"À medida que a especificação RISC-V ISA evolui e adiciona um número cada vez maior de extensões de arquitetura opcionais, torna-se essencial uma metodologia de design de processador que permite a exploração rápida da arquitetura e a criação simplificada de RTL facilmente implementável", observou Chris Jones, vice-presidente de Marketing na Codasip. "O que é necessário é uma linguagem de descrição de processador de alto nível otimizada para o RISC-V", acrescentou, apresentando o conjunto de ferramentas.

A descrição do processador é escrita em CodAL, uma linguagem de descrição da arquitetura e, em seguida, o RTL do projeto, o banco de testes, os modelos de plataforma virtual e o kit de desenvolvimento de software do processador (compilador C / C ++, depurador, criador de perfil) são automaticamente sintetizados. A metodologia reduz o tempo gasto com a manutenção de um kit completo de desenvolvimento de software (SDK) usando um modelo de processador de instruções precisas (IA) no CodAL to Time, que seria necessário para manter um SDK completo e a implementação é significativamente reduzida graças à metodologia usada um modelo de processador de instrução precisa (IA) no CodAL para geração de SDK e um modelo de ciclo preciso para implementação.

Novas funcionalidades e recursos para o conjunto de ferramentas de oitava geração incluem suporte para um depurador LLVM e OpenOCB, IDEs (ambientes de desenvolvimento integrado) Studio / CodeSpace baseados no Eclipse Oxygen e consoles e melhorias mais interativos nos conjuntos de testes e verificação para suportar RISC definido pelo usuário Extensões -V.

A empresa também introduziu o processador Bk7 de 64 bits, adicionando à família Bk. Possui um pipeline de sete estágios com previsão de ramificação, unidade de gerenciamento de memória completa opcional (MMU) com suporte a endereçamento virtual para sistemas operacionais como Linux, extensões padrão RISC-V populares e interfaces externas padrão do setor.

É o processador de mais alto desempenho da empresa até o momento e é personalizável para que os desenvolvedores adicionem instruções, registros ou interfaces.

O Studio 8 e o processador Bk7 estarão geralmente disponíveis no primeiro trimestre de 2019, com acesso antecipado a clientes selecionados imediatamente.

A Microchip anunciou que está adicionando o que acredita ser a primeira arquitetura RISC-V SoC FPGA do setor ao seu ecossistema Mi-V. Os FPGAs combinam os FPGAs Microsemiconductor PolarFire e um subsistema de microprocessador baseado no RISC-V ISA.

Antes da Cúpula, a Linux Foundation anunciou sua colaboração com a RISC-V Foundation para acelerar o desenvolvimento de código aberto e a adoção do RISC-V ISA.