ข่าว

มุมมองจากการประชุมสุดยอด RISC-V

มีการประกาศสองครั้งจากระบบ IAR เพื่อสนับสนุนการสร้างระบบนิเวศที่แข็งแกร่งสำหรับ RISC-V สิ่งแรกคือกับ SiFive ผู้ให้บริการ IP เพื่อร่วมมือกันในการนำเครื่องมือคอมไพเลอร์และดีบั๊กของอดีตไปยัง IP core ของโปรเซสเซอร์ที่กำหนดค่าได้

คาดว่าการรวมเครื่องมือและ IP จะช่วยสนับสนุนนักพัฒนาเพื่อส่งมอบผลิตภัณฑ์และเพื่อเพิ่มการปรับใช้สถาปัตยกรรมชุดคำสั่ง (ISA) แบบเปิดฟรี

Anders Holmberg ประธานเจ้าหน้าที่ฝ่ายกลยุทธ์ของ IAR Systems กล่าวว่าเป้าหมายคือเพื่อช่วยให้นักพัฒนาเพิ่มผลผลิตและมุ่งเน้นไปที่นวัตกรรม “ SiFive เป็นผู้นำในการค้า RISC-V core IP และ toolchain ของเรา IAR Embedded Workbench เป็นเครื่องมือที่ใช้กันอย่างแพร่หลายสำหรับการสร้างแอพพลิเคชั่นที่ฝังตัว” เขากล่าว สำเนียงนี้อยู่บนซิลิคอนที่กำหนดเองได้อย่างมีประสิทธิภาพและเครื่องมือในการพัฒนาเพื่อตอบสนองการคำนวณปริมาณงาน

IAR Embedded Workbench สำหรับ RISC-V จะมีวางจำหน่ายในช่วงกลางปี 2019 Toolchain อ้างว่าให้ "คุณภาพรหัสขนาดและความเร็ว" ชั้นนำรวมถึงดีบักเกอร์ในตัวพร้อมตัวจำลองและการสนับสนุนการดีบักฮาร์ดแวร์

บริษัท ซอฟต์แวร์ยังได้ประกาศความร่วมมือกับผู้ให้บริการ CPU IP Andes เพื่อสนับสนุนแกน RISC-V ของ บริษัท , AndesCore N25 (F) / NX25 (F) และ A25 / AX25 ใน IAR Embedded Workbench สำหรับ RISC-V รุ่นแรกจะวางตลาดในกลางปี 2019 ความสามารถในการปรับแต่งคำสั่ง AndeStar V5 และความสามารถในการปรับแต่งคำสั่ง Andes Custom Extension (ACE) จะถูกนำมารวมกับ Workbench เพื่อเพิ่มความเร็วโค้ดสูงสุดและลดขนาดรหัสสำหรับแกน RISC-V

ระบบอัตโนมัติและการคำนวณแบบเรียลไทม์

ชุดเครื่องมือรุ่นล่าสุดและแกน EOSC-V ใหม่ที่ได้รับการปรับให้เหมาะสมสำหรับ Linux และการประมวลผลแบบเรียลไทม์ได้รับการประกาศโดย Codasip

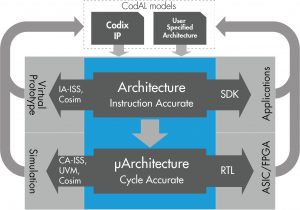

ชุดเครื่องมือ Studio 8 ช่วยให้นักพัฒนาสามารถเขียนคำอธิบายระดับสูงของโปรเซสเซอร์และสังเคราะห์การออกแบบ (ภาพ) โดยอัตโนมัติ

“ เมื่อข้อมูลจำเพาะ RISC-V ISA วิวัฒนาการและเพิ่มจำนวนของส่วนขยายสถาปัตยกรรมทางเลือกวิธีการออกแบบโปรเซสเซอร์ที่ช่วยให้การสำรวจสถาปัตยกรรมอย่างรวดเร็วและการสร้าง RTL ที่ใช้งานได้ง่ายกลายเป็นสิ่งจำเป็น” Chris Jones รองประธาน บริษัท การตลาดที่ Codasip “ สิ่งที่จำเป็นคือภาษาคำอธิบายโปรเซสเซอร์ระดับสูงที่ปรับให้เหมาะกับ RISC-V” เขากล่าวเสริมโดยแนะนำชุดเครื่องมือ

คำอธิบายหน่วยประมวลผลเขียนใน CodAL ภาษาคำอธิบายสถาปัตยกรรมจากนั้น RTL, ม้านั่งทดสอบ, โมเดลแพลตฟอร์มเสมือนและชุดพัฒนาซอฟต์แวร์โปรเซสเซอร์ (C / C ++ คอมไพเลอร์, ดีบั๊ก, ผู้สร้างโปรไฟล์) โดยอัตโนมัติ วิธีการลดเวลาที่ใช้ในการบำรุงรักษาชุดพัฒนาซอฟต์แวร์ (SDK) โดยใช้โมเดลตัวประมวลผลคำสั่ง (IA) ที่ถูกต้องใน CodAL to Time ซึ่งจะต้องมีการบำรุงรักษา SDK ที่สมบูรณ์และลดการใช้งานอย่างมากด้วยวิธีการที่ใช้ โมเดลตัวประมวลผลคำสั่ง (IA) ที่ถูกต้องใน CodAL สำหรับการสร้าง SDK และโมเดลที่แม่นยำรอบสำหรับการใช้งาน

ฟังก์ชั่นและคุณสมบัติใหม่สำหรับชุดเครื่องมือรุ่นที่แปดนั้นรวมถึงการรองรับ LLVM ดีบักเกอร์และ OpenOCB, สภาพแวดล้อมการพัฒนาแบบบูรณาการของ Studio / CodeSpace (IDEs) บนพื้นฐานของ Eclipse Oxygen และคอนโซลการโต้ตอบและการปรับปรุงเพิ่มเติมสำหรับชุดทดสอบ -V ส่วนขยาย

บริษัท ยังได้เปิดตัวโปรเซสเซอร์ Bk7 64 บิตซึ่งเพิ่มเข้ามาในตระกูล Bk มันมีไปป์ไลน์เจ็ดขั้นตอนพร้อมการคาดเดาสาขาหน่วยการจัดการหน่วยความจำเต็ม (MMU) ซึ่งเป็นทางเลือกพร้อมด้วยการสนับสนุนการกำหนดแอดเดรสเสมือนสำหรับระบบปฏิบัติการเช่น Linux ส่วนขยายมาตรฐาน RISC-V ยอดนิยมและอินเทอร์เฟซภายนอกมาตรฐานอุตสาหกรรม

เป็นโปรเซสเซอร์ที่มีประสิทธิภาพสูงสุดของ บริษัท จนถึงปัจจุบันและสามารถปรับแต่งได้สำหรับนักพัฒนาเพื่อเพิ่มคำแนะนำการลงทะเบียนหรืออินเทอร์เฟซ

โดยทั่วไปแล้วโปรเซสเซอร์ Studio 8 และ Bk7 จะวางจำหน่ายในช่วงไตรมาสแรกของปี 2019 โดยมีการเข้าถึงลูกค้าที่ได้รับการคัดเลือกทันที

Microchip ประกาศว่าจะเพิ่มสิ่งที่เชื่อว่าเป็นสถาปัตยกรรม RISC-V SoC FPGA แรกของอุตสาหกรรมในระบบนิเวศ Mi-V FPGA รวม Microsem Semiconductoror PolarFire FPGAs และระบบย่อยไมโครโปรเซสเซอร์ตาม RISC-V ISA

ก่อนหน้าการประชุมสุดยอด Linux Foundation ประกาศความร่วมมือกับมูลนิธิ RISC-V เพื่อเร่งการพัฒนาโอเพนซอร์ซและการนำ RISC-V ISA มาใช้