hírek

Kilátás a RISC-V csúcstalálkozóról

Az IAR Systems két bejelentést tett egy erős ökoszisztéma létrehozásának támogatásáról a RISC-V számára. Az elsõ az IP szolgáltatóval, a SiFive-vel volt, hogy együttmûködjenek az elõbbi fordító és hibakeresõ eszközeinek a konfigurálható processzor mag IP-jére való átalakításában.

Az eszközök és az IP integrációja várhatóan támogatja a fejlesztőket a termékek szállításában, és fokozza a nyílt, ingyenes utasításkészlet-architektúra (ISA) telepítését.

Anders Holmberg, az IAR Systems stratégiai vezérigazgatója azt mondta, hogy célja a fejlesztőknek a termelékenység növelésében és az innovációra való összpontosítás elősegítése. "A SiFive vezető szerepet játszik a kereskedelmi RISC-V mag IP-jében, és az IAR Embedded Workbench szerszámláncunk a legszélesebb körben alkalmazott eszközlánc beágyazott alkalmazások készítéséhez" - mondta. A hangsúly a méretezhető, hatékony egyedi szilícium és fejlesztőeszközök, amelyek megfelelnek a számítási munkaterhelésnek.

Az IAR beágyazott munkapad a RISC-V-hez 2019 közepén lesz elérhető. Az eszközlánc azt állítja, hogy „vezető kódminőséget, méretet és sebességet” kínál, valamint egy integrált hibakeresőt szimulátor és hardver hibakeresési támogatással.

A szoftverfejlesztő társaság emellett bejelentette a partnerséget az Andes CPU IP szolgáltatóval, hogy támogassa a vállalat RISC-V magjait, az AndesCore N25 (F) / NX25 (F) és A25 / AX25-et az IAR Embedded Workbench-ben a RISC-V számára. Az első verzió 2019 közepén lesz elérhető. Az AndeStar V5 utasítások kiterjesztése és az Andes Custom Extension (ACE) utasítások testreszabási képességei a Workbench alkalmazásával lesznek összekapcsolva a kódsebesség maximalizálása és a RISC-V magok kódméretének minimalizálása érdekében.

Automatizálás és valós idejű számítástechnika

A Codasip bejelentette szerszámcsomagjának legújabb verzióját és egy új EOSC-V magot, amely a Linuxra és a valósidejű számításra lett optimalizálva.

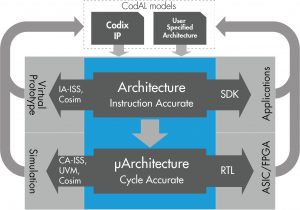

A Studio 8 eszközkészlet lehetővé teszi a fejlesztőknek, hogy magas szintű leírást írjanak le a processzorról, és automatikusan szintetizálják a tervezést (a képen).

„Ahogy a RISC-V ISA specifikáció fejlődik és egyre növekszik az opcionális architektúra-kiterjesztések száma, elengedhetetlenné válik a processzor-tervezési módszer, amely lehetővé teszi mind a gyors építészeti felfedezést, mind pedig a könnyen megvalósítható RTL egyszerűsített létrehozását” - jegyezte meg Chris Jones, a Marketing a Codasipnél. „Szükség van egy magas szintű processzorleíró nyelvre, amely a RISC-V számára lett optimalizálva” - tette hozzá az eszközkészlet bemutatása.

A processzor leírását CodAL-ban, egy architektúra leíró nyelven írják, majd automatikusan szintetizálják a terv RTL-jét, tesztpadját, virtuális platformmodelleit és a processzor szoftverfejlesztő készletét (C / C ++ fordító, hibakereső, profilkészítő). A módszertan csökkenti a teljes szoftverfejlesztő készlet (SDK) fenntartására fordított időt azáltal, hogy egy utasítás pontos (IA) processzormodellt alkalmaz a CodAL-Time-ban, amely egyébként a teljes SDK fenntartásához lenne szükséges, és a megvalósítás jelentősen csökken a felhasznált módszertannak köszönhetően utasítás pontos (IA) processzor modell a CodAL-ban az SDK generálásához és a ciklus pontos modell a megvalósításhoz.

A nyolcadik generációs eszközkészlet új funkciói és szolgáltatásai között szerepel az LLVM hibakereső és az OpenOCB, az Eclipse Oxygen alapú Studio / CodeSpace integrált fejlesztési környezetek (IDE), valamint az interaktív konzolok fejlesztése, valamint a tesztcsomagok fejlesztése és az ellenőrzés a felhasználó által definiált RISC támogatása érdekében. -V kiterjesztések.

A cég bevezette a 64 bites Bk7 processzort is, kiegészítve a Bk családot. Hétfokozatú csővezetékkel rendelkezik, ágazati előrejelzéssel, opcionális teljes memóriakezelő egységgel (MMU), virtuális címtámogatással olyan operációs rendszerekre, mint a Linux, a népszerű RISC-V standard kiterjesztések és az ipari szabványú külső interfészek.

Ez a vállalat eddig legnagyobb teljesítményű processzora, és a fejlesztők számára testreszabható, hogy utasításokat, nyilvántartásokat vagy interfészeket adjon hozzá.

A Studio 8 és a Bk7 processzor általánosságban elérhető lesz 2019. év első negyedévében, a kiválasztott ügyfelek számára pedig korai hozzáféréssel azonnal elérhetők.

A Microchip bejelentette, hogy a Mi-V ökoszisztémájához hozzáadja azt, amelyet véleménye szerint az iparág első RISC-V SoC FPGA architektúrája. Az FPGA-k egyesítik a Microsemiconductor PolarFire FPGA-kat és a RISC-V ISA-n alapuló mikroprocesszoros alrendszert.

A csúcstalálkozó előtt a Linux Alapítvány bejelentette együttműködését a RISC-V Alapítvánnyal a RISC-V ISA nyílt forráskódú fejlesztésének és elfogadásának felgyorsítása érdekében.