Tin tức

Một cái nhìn từ Hội nghị thượng đỉnh RISC-V

Có hai thông báo từ IAR Systems để hỗ trợ thiết lập một hệ sinh thái mạnh mẽ cho RISC-V. Đầu tiên là với nhà cung cấp IP, SiFive, để hợp tác trong việc đưa các công cụ gỡ lỗi và trình biên dịch cũ trước đây vào IP lõi của bộ xử lý có thể cấu hình.

Việc tích hợp các công cụ và IP dự kiến sẽ hỗ trợ các nhà phát triển phân phối sản phẩm và tăng cường triển khai kiến trúc tập lệnh mở, miễn phí (ISA).

Anders Holmberg, Giám đốc Chiến lược, IAR Systems, cho biết mục đích là giúp các nhà phát triển tăng năng suất và tập trung vào đổi mới. Ông Si Siive là một nhà lãnh đạo trong IP lõi RISC-V thương mại và chuỗi công cụ IAR Embedded Workbench của chúng tôi là chuỗi công cụ được sử dụng rộng rãi nhất để xây dựng các ứng dụng nhúng, ông nói. Điểm nhấn là các công cụ phát triển và silicon tùy chỉnh hiệu quả có thể mở rộng để đáp ứng khối lượng công việc tính toán.

Bàn làm việc nhúng IAR cho RISC-V sẽ có sẵn vào giữa năm 2019. Toolchain tuyên bố sẽ cung cấp chất lượng, kích thước và tốc độ mã hàng đầu của thế giới cũng như một trình gỡ lỗi tích hợp với hỗ trợ giả lập và gỡ lỗi phần cứng.

Công ty phần mềm cũng tuyên bố hợp tác với nhà cung cấp CPU IP, Andes, để hỗ trợ các lõi của công ty RISC-V, AndesCore N25 (F) / NX25 (F) và A25 / AX25, trong IAR Embedded Workbench cho RISC-V. Phiên bản đầu tiên sẽ có mặt vào giữa năm 2019. Các phần mở rộng lệnh của AndeStar V5 và các khả năng tùy chỉnh lệnh của Andes Custom Extension (ACE) sẽ được kết hợp với Workbench để tối đa hóa tốc độ mã và giảm thiểu kích thước mã cho lõi RISC-V.

Tự động hóa và tính toán thời gian thực

Phiên bản mới nhất của bộ công cụ của nó và lõi EOSC-V mới được tối ưu hóa cho Linux và tính toán thời gian thực đã được Codasip công bố.

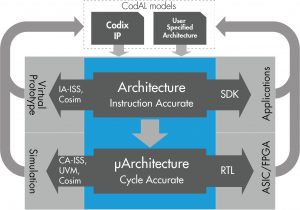

Bộ công cụ Studio 8 của nó cho phép các nhà phát triển viết một mô tả cấp cao về bộ xử lý và tự động tổng hợp thiết kế (trong hình).

Khi đặc tả kỹ thuật của RISC-V ISA phát triển và bổ sung số lượng phần mở rộng kiến trúc tùy chọn ngày càng tăng, một phương pháp thiết kế bộ xử lý cho phép khám phá kiến trúc nhanh chóng và tạo ra đơn giản RTL dễ thực hiện trở nên thiết yếu, Chris Jones, Phó chủ tịch của Tiếp thị tại Codasip. Những gì cần thiết là một ngôn ngữ mô tả bộ xử lý cấp cao được tối ưu hóa cho RISC-V, ông đã thêm vào, giới thiệu bộ công cụ.

Mô tả bộ xử lý được viết bằng CodAL, một ngôn ngữ mô tả kiến trúc và sau đó, thiết kế của RT RTL, băng ghế thử nghiệm, mô hình nền tảng ảo và bộ phát triển phần mềm bộ xử lý (trình biên dịch C / C ++, trình gỡ lỗi, trình lược tả) được tự động tổng hợp. Phương pháp này giúp giảm thời gian duy trì bộ công cụ phát triển phần mềm (SDK) hoàn chỉnh bằng cách sử dụng mô hình bộ xử lý chính xác (IA) trong CodAL to Time, nếu không sẽ phải duy trì SDK hoàn chỉnh và việc triển khai được giảm đáng kể nhờ phương pháp sử dụng một mô hình bộ xử lý chính xác hướng dẫn (IA) trong CodAL để tạo SDK và một mô hình chính xác theo chu kỳ để thực hiện.

Các chức năng và tính năng mới cho bộ công cụ thế hệ thứ tám bao gồm hỗ trợ cho trình gỡ lỗi LLVM và môi trường phát triển tích hợp (IDE) của OpenOCB, Studio / CodeSpace dựa trên Oxygen Oxygen và các bảng điều khiển tương tác và cải tiến hơn cho các bộ kiểm tra và xác minh để hỗ trợ RISC do người dùng định nghĩa Phần mở rộng -V.

Công ty cũng giới thiệu bộ xử lý Bk7 64 bit, thêm vào gia đình Bk. Nó có một đường dẫn gồm bảy giai đoạn với dự đoán nhánh, đơn vị quản lý bộ nhớ đầy đủ tùy chọn (MMU) với hỗ trợ địa chỉ ảo cho các hệ điều hành như Linux, các phần mở rộng tiêu chuẩn RISC-V phổ biến và giao diện bên ngoài tiêu chuẩn công nghiệp.

Đây là bộ xử lý hiệu năng cao nhất của công ty, cho đến nay và có thể tùy chỉnh để các nhà phát triển thêm hướng dẫn, đăng ký hoặc giao diện.

Studio 8 và bộ xử lý Bk7 thường sẽ có sẵn Q1 2019, với quyền truy cập sớm vào các khách hàng được chọn ngay lập tức.

Microchip tuyên bố rằng họ đang bổ sung những gì nó tin là kiến trúc RISC-V SoC FPGA đầu tiên trong ngành vào hệ sinh thái Mi-V của mình. Các GPU kết hợp các vi phân cực PolarFire và các hệ thống con vi xử lý dựa trên RISC-V ISA.

Trước Hội nghị thượng đỉnh, Quỹ Linux đã tuyên bố hợp tác với Quỹ RISC-V để tăng tốc phát triển nguồn mở và áp dụng RISC-V ISA.