Notizie

Una vista dal vertice RISC-V

Ci sono stati due annunci da parte di IAR Systems a supporto della creazione di un ecosistema robusto per RISC-V. Il primo è stato con il provider IP, SiFive, a collaborare per portare gli strumenti del compilatore e del debugger precedenti all'IP core del processore configurabile.

Si prevede che l'integrazione di strumenti e IP supporterà gli sviluppatori a fornire prodotti e ad aumentare la diffusione dell'architettura di set di istruzioni (ISA) aperta e gratuita.

Anders Holmberg, Chief Strategy Officer, IAR Systems, ha affermato che l'obiettivo è aiutare gli sviluppatori a incrementare la produttività e concentrarsi sull'innovazione. "SiFive è leader nell'IP core RISC-V commerciale e la nostra toolchain IAR Embedded Workbench è la toolchain più utilizzata per la creazione di applicazioni integrate", ha affermato. L'accento è sul silicio personalizzato scalabile ed efficiente e sugli strumenti di sviluppo per soddisfare i carichi di lavoro di calcolo.

IAR Embedded Workbench per RISC-V sarà disponibile a metà 2019. La toolchain afferma di offrire "qualità, dimensioni e velocità del codice leader", nonché un debugger integrato con simulatore e supporto per il debug dell'hardware.

La società di software ha inoltre annunciato una partnership con Andes, fornitore di CPU IP, per supportare i core RISC-V dell'azienda, AndesCore N25 (F) / NX25 (F) e A25 / AX25, in IAR Embedded Workbench per RISC-V. La prima versione sarà disponibile a metà 2019. Le funzionalità di personalizzazione dell'istruzione AndeStar V5 extension e ACE (Andes Custom Extension) saranno abbinate a Workbench per massimizzare la velocità del codice e minimizzare le dimensioni del codice per i core RISC-V.

Automazione e elaborazione in tempo reale

L'ultima versione della sua suite di strumenti e un nuovo core EOSC-V ottimizzato per Linux e il calcolo in tempo reale sono stati annunciati da Codasip.

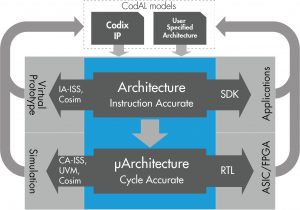

La sua suite di strumenti Studio 8 consente agli sviluppatori di scrivere una descrizione di alto livello di un processore e sintetizza automaticamente il design (nella foto).

"Con l'evolversi delle specifiche RISC-V ISA e l'aggiunta di un numero sempre crescente di estensioni di architettura opzionali, diventa essenziale una metodologia di progettazione del processore che consenta sia l'esplorazione rapida dell'architettura sia la creazione semplificata di RTL facilmente implementabile", ha osservato Chris Jones, Vice Presidente di Marketing presso Codasip. "È necessario un linguaggio di descrizione del processore di alto livello ottimizzato per RISC-V", ha aggiunto, introducendo la suite di strumenti.

La descrizione del processore è scritta in CodAL, un linguaggio di descrizione dell'architettura, quindi vengono automaticamente sintetizzati RTL del design, banco di prova, modelli di piattaforma virtuale e kit di sviluppo del software del processore (compilatore C / C ++, debugger, profiler). La metodologia riduce il tempo impiegato per mantenere un kit di sviluppo software completo (SDK) utilizzando un modello di processore accurato (IA) in CodAL to Time che altrimenti sarebbe necessario per mantenere un SDK completo e l'implementazione è significativamente ridotta grazie alla metodologia che utilizza un modello di processore accurato (IA) in CodAL per la generazione di SDK e un modello accurato per il ciclo per l'implementazione.

Le nuove funzionalità e caratteristiche per la suite di strumenti di ottava generazione includono il supporto per un debugger LLVM e OpenOCB, ambienti di sviluppo integrati Studio / CodeSpace (IDE) basati su Eclipse Oxygen e altre console interattive e miglioramenti alle suite di test e verifica per supportare RISC definito dall'utente -V estensioni.

La società ha anche introdotto il processore Bk7 a 64 bit, aggiungendo alla famiglia Bk. Ha una pipeline a sette stadi con previsione di diramazione, MMU (Full Memory Management Unit) opzionale con supporto di indirizzamento virtuale per sistemi operativi come Linux, estensioni standard RISC-V popolari e interfacce esterne standard di settore.

È il processore ad alte prestazioni dell'azienda fino ad oggi ed è personalizzabile per gli sviluppatori per aggiungere istruzioni, registri o interfacce.

Studio 8 e il processore Bk7 saranno generalmente disponibili nel primo trimestre del 2019, con accesso immediato ai clienti selezionati immediatamente.

Microchip ha annunciato che sta aggiungendo quella che ritiene essere la prima architettura FPGA SoC RISC-V del settore al suo ecosistema Mi-V. Gli FPGA combinano FPGA PolarFire a microsemiconduttore e un sottosistema a microprocessore basato sul RISC-V ISA.

Prima del vertice, la Linux Foundation ha annunciato la sua collaborazione con la RISC-V Foundation per accelerare lo sviluppo open source e l'adozione del RISC-V ISA.