Uutiset

Näkymä RISC-V-huippukokouksesta

IAR Systems ilmoitti kahdesta tukevan ekosysteemin perustamisen tukemisesta RISC-V: lle. Ensimmäinen oli IP-palveluntarjoajan, SiFive, kanssa yhteistyö tuodaan entisen kääntäjä- ja virheenkorjaustyökalut konfiguroitavissa olevaan prosessorin ydin-IP: hen.

Työkalujen ja IP: n integroinnin odotetaan tukevan kehittäjiä tuotteiden toimittamisessa ja lisäävän avoimen, ilmaisen käskyjoukkoarkkitehtuurin (ISA) käyttöönottoa.

IAR Systemsin strategiajohtaja Anders Holmberg kertoi, että tavoitteena on auttaa kehittäjiä lisäämään tuottavuutta ja keskittymään innovaatioihin. "SiFive on johtava kaupallisessa RISC-V-ydin-IP: ssä, ja työkaluketjun IAR Embedded Workbench on yleisimmin käytetty työkaluketju sulautettujen sovellusten rakentamiseen", hän sanoi. Painopiste on skaalautuvissa, tehokkaissa räätälöityissä piissä ja kehitystyökaluissa laskentataakkojen täyttämiseksi.

IAR-upotettu työpenkki RISC-V: lle on saatavana vuoden 2019 puolivälissä. Työkaluketju väittää tarjoavansa "johtavan koodin laadun, koon ja nopeuden" sekä integroidun virheenkorjaimen simulaattorilla ja laitteiston virheenkorjaustuella.

Ohjelmistoyritys ilmoitti myös kumppanuudesta CPU IP-palveluntarjoajan Andesin kanssa tukeakseen yrityksen RISC-V-ytimiä, AndesCore N25 (F) / NX25 (F) ja A25 / AX25, IAR Embedded Workbenchissa RISC-V: lle. Ensimmäinen versio on saatavilla vuoden 2019 puolivälissä. AndeStar V5 -käskylaajennus ja Andes Custom Extension (ACE) -käskyjen mukauttamisominaisuudet yhdistetään Workbenchiin maksimoidaksesi koodinopeuden ja minimoidaksesi koodikoko RISC-V-ytimille.

Automaatio ja reaaliaikainen laskenta

Codasip ilmoitti viimeisimmästä työkalusarjansa versiosta ja uuden EOSC-V-ytimen, joka on optimoitu Linuxille ja reaaliaikaiselle tietojenkäsittelylle.

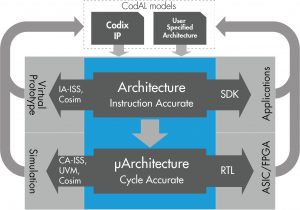

Sen Studio 8 -työkalupaketti antaa kehittäjille mahdollisuuden kirjoittaa korkean tason kuvaus prosessorista ja syntetisoida mallin automaattisesti (kuvassa).

"Kun RISC-V ISA -määrittely kehittyy ja lisää yhä enemmän valinnaisia arkkitehtuurin laajennuksia, prosessorin suunnittelumenetelmästä, joka mahdollistaa sekä nopean arkkitehtuurintutkimuksen että helposti toteutettavan RTL: n yksinkertaistetun luomisen, on välttämätöntä", totesi Chris Jones, varatoimitusjohtaja. Markkinointi Codasipissa. ”Tarvitaan korkean tason prosessorikieli, joka on optimoitu RISC-V: lle”, hän lisäsi työkalusarjaa esittelemällä.

Suorittimen kuvaus on kirjoitettu arkkitehtuurin kuvauskielellä CodAL, ja sitten syntetisoidaan automaattisesti suunnittelun RTL, testipenkki, virtuaalisen alustan mallit ja prosessorin ohjelmistokehityspaketti (C / C ++ -kokoonpano, virheenkorjaus, profiilisoija). Metodologia vähentää täydellisen ohjelmistokehityspaketin (SDK) ylläpitämiseen kuluvaa aikaa käyttämällä CODAL to Time -käskyn tarkkaa (IA) prosessorimallia, jota muuten vaaditaan täydellisen SDK: n ylläpitämiseksi ja toteutus vähenee huomattavasti metodologian avulla, joka käyttää käskytarkka (IA) prosessorimalli CodAL: ssa SDK-generointiin ja jaksotarkka malli toteutusta varten.

Kahdeksannen sukupolven työkalupaketin uusia toimintoja ja ominaisuuksia ovat tuki LLVM-virheenkorjaimelle ja OpenOCB-, Studio / CodeSpace-integroiduille kehitysympäristöille (IDE), jotka perustuvat Eclipse Oxygen -ympäristöön, ja vuorovaikutteisempiin konsoliin sekä parannuksia testipaketteihin ja todentamista käyttäjän määrittelemän RISC: n tukemiseksi. -V laajennukset.

Yhtiö esitteli myös 64-bittisen Bk7-prosessorin, joka lisäsi Bk-perhettä. Siinä on seitsemän vaiheen putkilinja, jolla on haaraennuste, valinnainen täyden muistin hallintayksikkö (MMU), jossa on virtuaalinen osoitustuki käyttöjärjestelmille, kuten Linux, suositut RISC-V-vakiolaajennukset ja alan standardin mukaiset ulkoiset rajapinnat.

Se on yrityksen tähän mennessä tehokkain prosessori, ja se on räätälöitävissä kehittäjille lisäämään ohjeita, rekistereitä tai käyttöliittymiä.

Studio 8 ja Bk7-prosessori ovat yleensä saatavana Q1 2019, ja he pääsevät varhaisessa vaiheessa valittuihin asiakkaisiin heti.

Mikrosiru ilmoitti lisäävänsä Mi-V-ekosysteemiin, jonka se uskoo olevan alan ensimmäinen RISC-V SoC FPGA -arkkitehtuuri. FPGA: t yhdistävät Microsemiconductor PolarFire FPGA: t ja RISC-V ISA: een perustuvan mikroprosessorin alijärjestelmän.

Huippukokouksen edessä Linux-säätiö ilmoitti tekevänsä yhteistyötä RISC-V-säätiön kanssa avoimen lähdekoodin kehittämisen ja RISC-V ISA: n käyttöönoton nopeuttamiseksi.