Tin tức

SureCore thêm trình biên dịch bộ nhớ FDSOI

Trình biên dịch hỗ trợ công ty công suất thấp, cổng SRAM IP đơn và cổng SRAM IP kép cho công nghệ xử lý FDSOI 28nm. Nó cung cấp dung lượng lên tới 1Mbit với độ dài từ lên tới 288 bit và hỗ trợ các yếu tố 4, 8 và 16 Mux.

Theo công ty, nó cho phép các nhà thiết kế thực hiện đánh đổi giữa các kích thước SRAM khác nhau về số lượng từ, độ dài từ và hệ số ghép, và tự động tạo ra các bảng dữ liệu, mô phỏng (Verilog), bố cục (LEF) và thời gian / sức mạnh (Liberty) các mô hình để tăng cường và tăng tốc quá trình thiết kế.

Trình biên dịch này nhắm đến IoT và các ứng dụng khác đòi hỏi thời lượng pin dài với hiệu suất hoạt động và năng lượng dự phòng tối thiểu và sẽ có giá trị trong không gian mạng nơi năng lượng và tản nhiệt rất quan trọng.

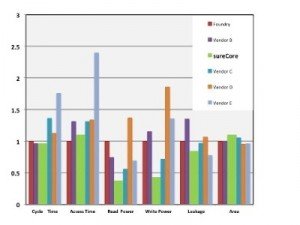

IP hỗ trợ dải điện áp hoạt động 0,6V-1,2V và tiết kiệm năng lượng động vượt quá 50% các dịch vụ thương mại khác, trong khi Công suất tĩnh cắt giảm tới 35% chỉ với một <10% area penalty, claims the company.

SureCore cho biết họ sẽ theo trình biên dịch FDSOI 28nm với trình biên dịch công suất cực thấp 40nm vào tháng 3, sẽ nhắm vào quy trình đúc hàng đầu. Lộ trình sản phẩm của công ty cũng bao gồm việc giới thiệu SRAM công suất cực thấp 40nm CMOS vào cuối năm tới. Công việc cũng tiếp tục trên một giải pháp CMOS 28nm.

Vẫn còn có sự đổi mới đáng kể xảy ra tại các nút sản xuất tương đối trưởng thành, Paul nói, CEO của SureCore, Paul Wells. Với thị trường IoT đang phát triển, các nút trưởng thành như 40nm là 28nm đang có tuổi thọ kéo dài. Hiệu suất chi phí của họ là lý tưởng cho các thách thức kinh doanh và kỹ thuật IoT.

Đọc thêm chắc chắn Câu chuyện khác trên Tuần báo Điện tử »