Noticias

sureCore agrega el compilador de memoria FDSOI

El compilador admite la baja potencia de la compañía, SRAM IP de un solo puerto y SRAM IP de doble puerto para la tecnología de proceso FDSOI de 28nm. Ofrece capacidades de hasta 1Mbit con longitudes de palabra de hasta 288bits y admite 4, 8 y 16 factores Mux.

Según la compañía, permite a los diseñadores hacer compensaciones entre varios tamaños de SRAM en términos de número de palabras, longitud de palabra y factor multiplex, y genera automáticamente hojas de datos, simulación (Verilog), diseño (LEF) y tiempo / potencia (Liberty) modelos para mejorar y acelerar el proceso de diseño.

El compilador está dirigido a IoT y otras aplicaciones que exigen una batería de larga duración con un rendimiento operativo mínimo y de energía en espera, y será valioso en el espacio de red donde la energía y la disipación de calor son críticas.

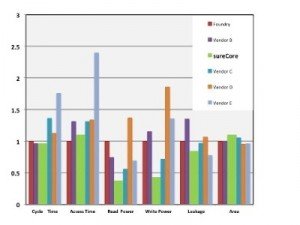

El IP admite un rango de voltaje operativo de 0.6V-1.2V y ahorros de energía dinámicos que exceden el 50% de otras ofertas comerciales, mientras que corta la energía estática hasta en un 35% con solo un <10% area penalty, claims the company.

SureCore dice que seguirá el compilador FDSOI de 28nm con un compilador de ultra baja potencia de 40nm en marzo, que se centrará en el proceso de fundición líder. La hoja de ruta de productos de la compañía también incluye la introducción de una SRAM CMOS de ultra baja potencia de 40 nm a finales del año próximo. El trabajo también continúa en una solución CMOS de 28 nm.

"Todavía se está produciendo una innovación considerable en nodos de producción relativamente maduros", dijo Paul Wells, CEO de sureCore. “Con el creciente mercado de IoT, los nodos maduros como 40nm son 28nm están adquiriendo una vida más larga. Su rentabilidad es ideal para los desafíos técnicos y comerciales de IoT ".

Lea más historias de sureCore en Electronics Weekly »