Balita

sureCore nagdadagdag ng compiler ng memorya ng FDSOI

Sinusuportahan ng tagatala ang mababang lakas, solong port SRAM IP at dalawahan na port SRAM IP para sa 28nm FDSOI process na teknolohiya. Nag-aalok ito ng mga kapasidad hanggang sa 1Mbit na may haba ng salita hanggang sa 288bits at sumusuporta sa 4, 8 at 16 Mux factor.

Ayon sa kumpanya pinapayagan ang mga taga-disenyo na gumawa ng mga trade-off sa pagitan ng iba't ibang laki ng SRAM sa mga tuntunin ng bilang ng mga salita, haba ng salita at factor ng multiplex, at awtomatikong bumubuo ng mga datasheet, simulation (Verilog), layout (LEF) at tiyempo / kapangyarihan (Liberty) mga modelo upang mapahusay at mapabilis ang proseso ng disenyo.

Ang tagatala ay naglalayong IoT at iba pang mga aplikasyon na humihiling ng mahabang buhay ng baterya na may minimal na operating at stand-by na pagganap ng kuryente at magiging mahalaga sa puwang ng networking kung saan kritikal ang kapangyarihan at init.

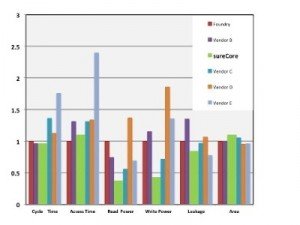

Sinusuportahan ng IP ang isang operating boltahe ng operating ng 0.6V-1.2V at dynamic na pag-iimpok ng kapangyarihan na lumampas sa 50% ng iba pang mga alay sa komersyal, habang ang Pagputol ng static na kapangyarihan ng hanggang sa 35% na may lamang isang <10% area penalty, claims the company.

Sinasabi ng SureCore na susundin nito ang 28nm FDSOI compiler na may 40nm ultra low power compiler sa Marso, na target nito ang nangungunang proseso ng pagsagip. Kasama rin sa roadmap ng kumpanya ang pagpapakilala ng isang 40nm CMOS ultra low power SRAM sa susunod na taon. Nagpapatuloy din ang trabaho sa isang 28nm na solusyon ng CMOS.

"Mayroon pa ring malaking pagbabago na nangyayari sa medyo mature na node ng produksyon," sabi ng sureCore's CEO, Paul Wells. "Sa lumalagong merkado ng IoT, ang mga mature node tulad ng 40nm ay 28nm ay tumatagal ng isang mahabang buhay. Ang kanilang pagganap sa gastos ay mainam para sa mga hamon sa teknikal at negosyo sa IoT. "

Magbasa nang higit pa siguradong Mga Kwento sa Elektroniko Lingguhan »